Y12T91 Arista:下一代AI网络的光模块采用热插拔还是CPO?

专属客服号

微信订阅号

-

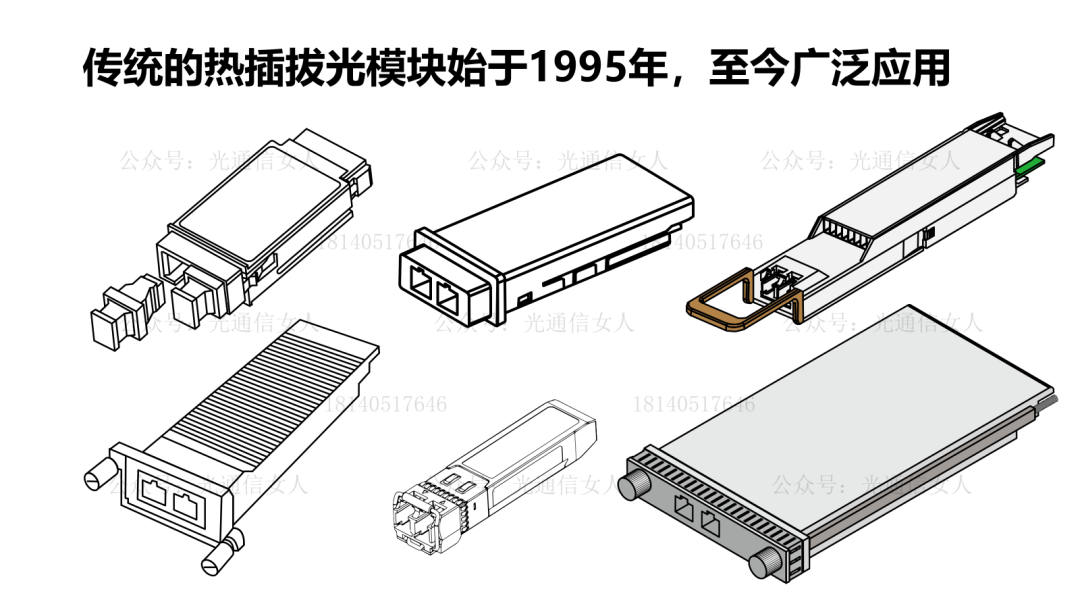

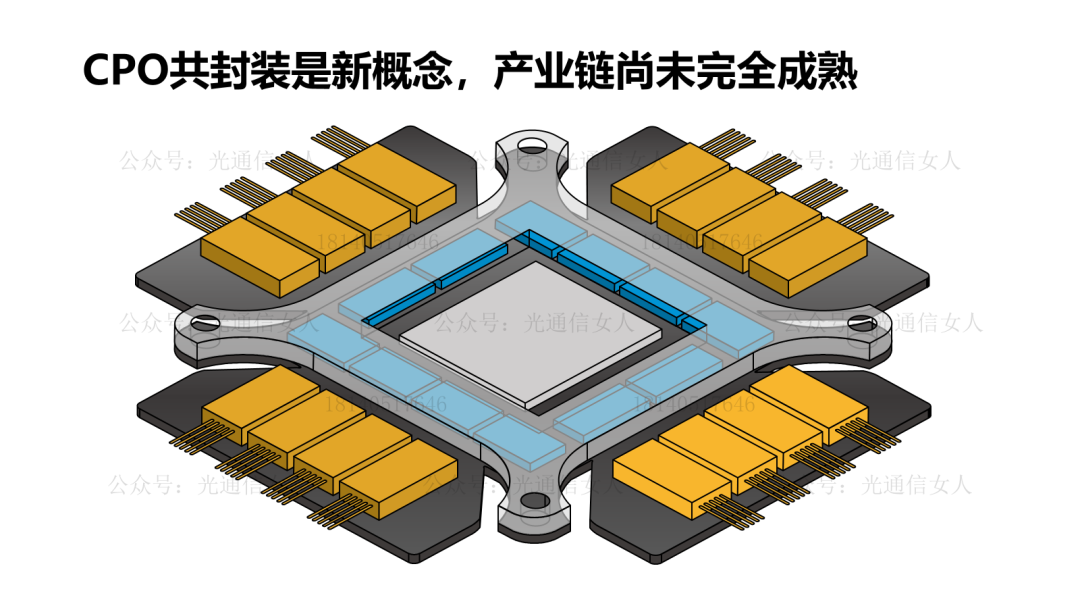

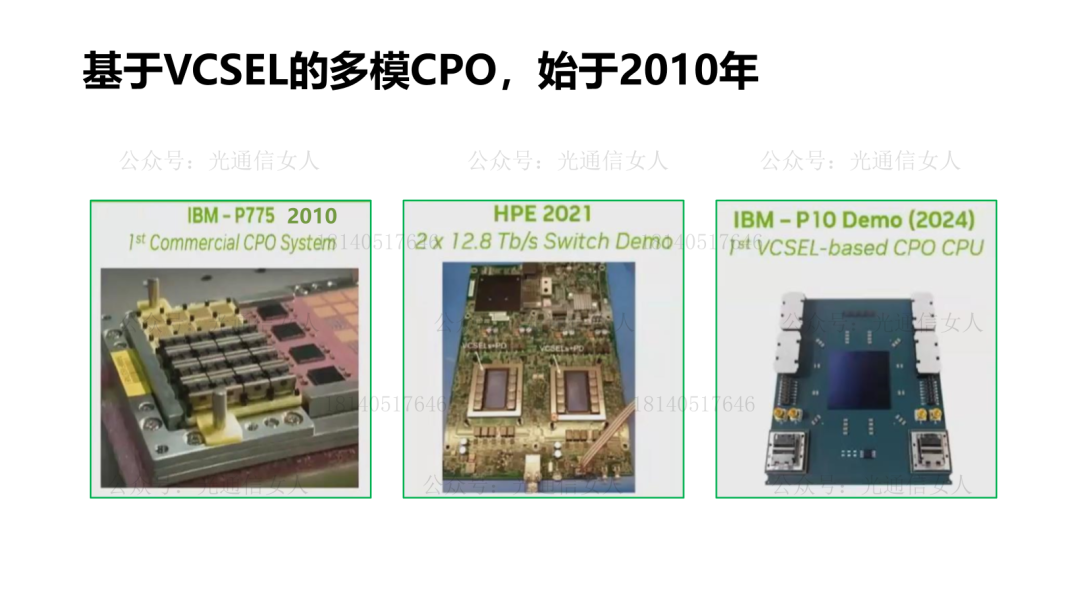

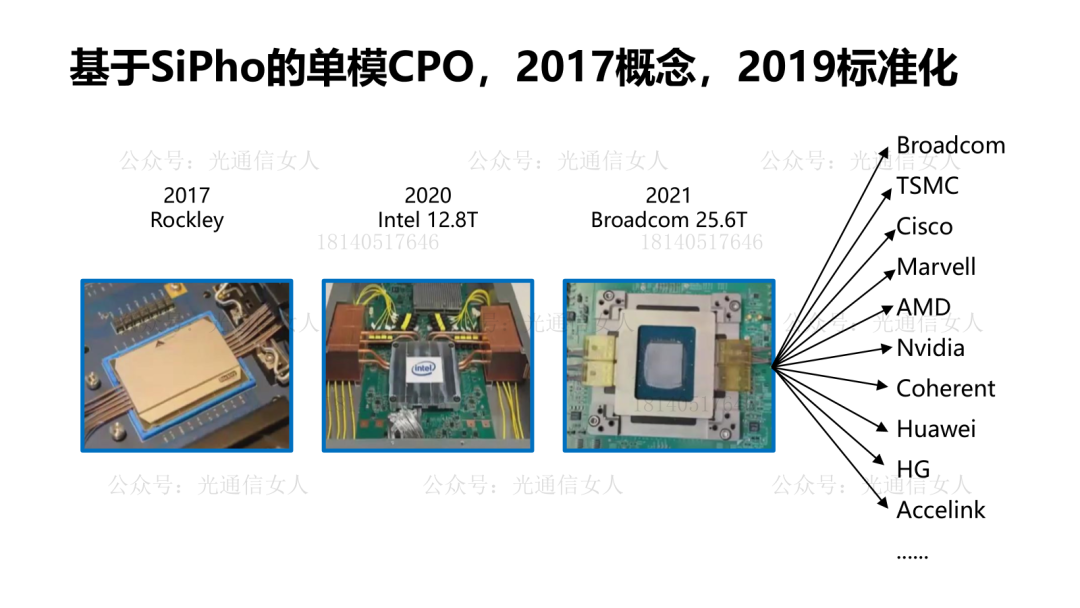

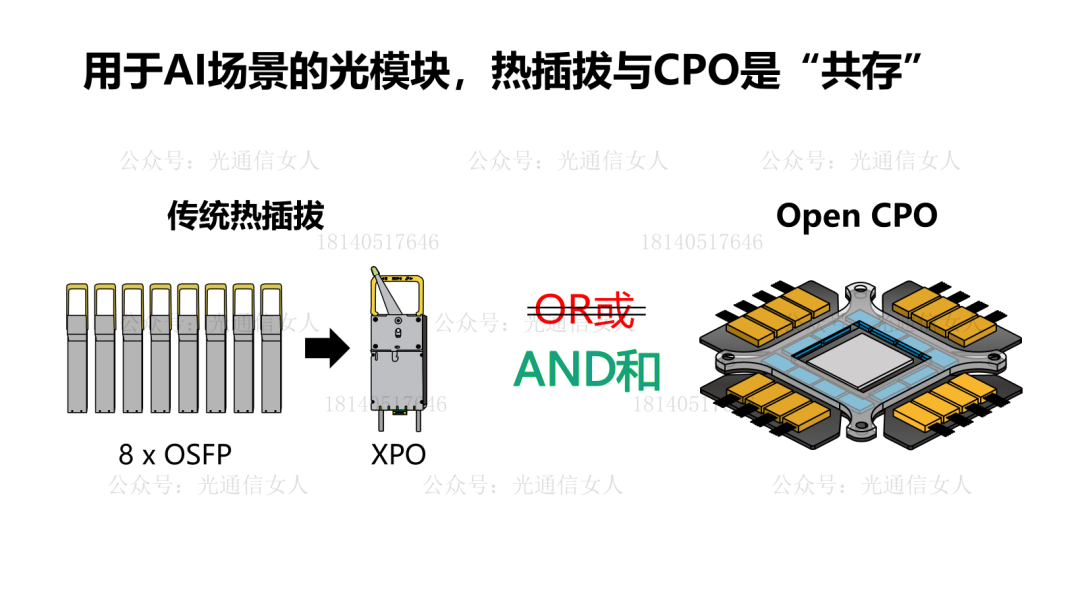

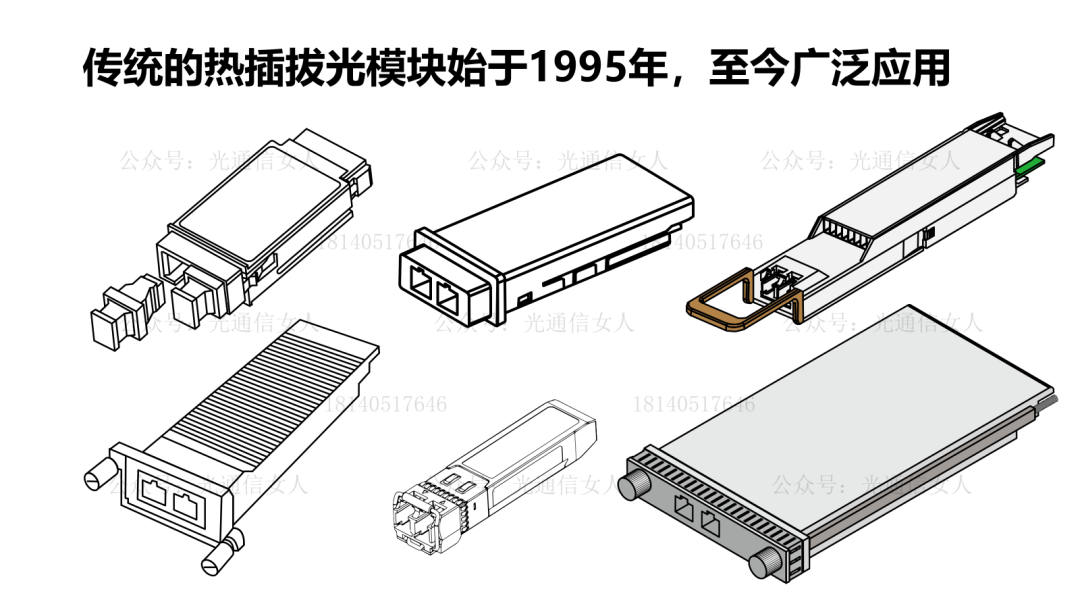

2026年的OFC,其中一个Workshop在讨论下一代用于AI的光学组网,采用传统的热插拔结构,还是CPO共封装光学。很多个厂家发表了自己的观点,今天先写一下Arista的看法。光模块的功能是光电信号转换,传统的热插拔结构始于1995年,互联网开始的时代,很多个人电脑需要上网。热插拔可以方便的“带电插入或拔出”,无需交换机系统断电。至今热插拔光模块依然广泛应用在光通信,成为传统结构。 热插拔光模块在2013年后随着数据中心的崛起,大带宽的热插拔结构开始增加了DSP芯片,导致光模块的功耗进一步增大。2023年-今,产业开始AI组网结构的800G、1.6T等更大容量的光模块进入规模部署阶段,光模块的功耗与热的困境,越来越凸显。一个是去掉DSP的LPO思路,可降低功耗且依然保持“热插拔”外型结构,能沿用传统光模块封装产业链。这个结构目前进展到12.8T XPO,在Y12T86写的。 另一个是去掉DSP的CPO(NPO)思路,可以降低功耗,且将OE引擎挪到系统侧,缩短ASIC芯片到OE的传输长度,改善电信号传输损耗。相比较传统的热插拔结构,CPO属于“新”概念,产业链这些年逐步成熟,但尚未达到热插拔的那个成熟度。说CPO很新,是相对的新,2010年IBM和finisar(现在的Coherent)就在研究基于多模的共封装技术。这一个系列,产业一直是有进展的基于硅光集成的单模CPO,在2017年OFC,Rockley就展出这种结构的初期概念。2018-2019产业链一些厂家如微软等开始筹备多源协议的标准化工作,后来OIF在2023年发布了第一版标准结构。2025年,Nvidia宣布采用CPO用于AI组网,这个概念就开始热闹起来。硅光方案的CPO呢,进入到商用探索期遇到的问题,与多模方案2010年遇到的问题很像,就是共封装的高密度下光机电热的新工艺如何“可靠”实现。目前,CPO高密度封装遇到的翘曲问题,依然在解决,我写过思科、台积电、博通、GF、AMF....等厂家对于翘曲的处理,CPO高密度封装的散热问题,产业链也在逐步解决,要解决散热路径和效率,要解决耐热性问题。这也是玻璃基板开始进入各大厂视野的一个原因。还有,CPO与光纤阵列的耦合问题,外置光源的保偏光纤的耦合问题,使用低功耗微环调制器的波长稳定性的问题,内置激光器的混合集成工艺等等等等。看一下Nvidia关注的几个CPO的技术优化方向。

热插拔光模块在2013年后随着数据中心的崛起,大带宽的热插拔结构开始增加了DSP芯片,导致光模块的功耗进一步增大。2023年-今,产业开始AI组网结构的800G、1.6T等更大容量的光模块进入规模部署阶段,光模块的功耗与热的困境,越来越凸显。一个是去掉DSP的LPO思路,可降低功耗且依然保持“热插拔”外型结构,能沿用传统光模块封装产业链。这个结构目前进展到12.8T XPO,在Y12T86写的。 另一个是去掉DSP的CPO(NPO)思路,可以降低功耗,且将OE引擎挪到系统侧,缩短ASIC芯片到OE的传输长度,改善电信号传输损耗。相比较传统的热插拔结构,CPO属于“新”概念,产业链这些年逐步成熟,但尚未达到热插拔的那个成熟度。说CPO很新,是相对的新,2010年IBM和finisar(现在的Coherent)就在研究基于多模的共封装技术。这一个系列,产业一直是有进展的基于硅光集成的单模CPO,在2017年OFC,Rockley就展出这种结构的初期概念。2018-2019产业链一些厂家如微软等开始筹备多源协议的标准化工作,后来OIF在2023年发布了第一版标准结构。2025年,Nvidia宣布采用CPO用于AI组网,这个概念就开始热闹起来。硅光方案的CPO呢,进入到商用探索期遇到的问题,与多模方案2010年遇到的问题很像,就是共封装的高密度下光机电热的新工艺如何“可靠”实现。目前,CPO高密度封装遇到的翘曲问题,依然在解决,我写过思科、台积电、博通、GF、AMF....等厂家对于翘曲的处理,CPO高密度封装的散热问题,产业链也在逐步解决,要解决散热路径和效率,要解决耐热性问题。这也是玻璃基板开始进入各大厂视野的一个原因。还有,CPO与光纤阵列的耦合问题,外置光源的保偏光纤的耦合问题,使用低功耗微环调制器的波长稳定性的问题,内置激光器的混合集成工艺等等等等。看一下Nvidia关注的几个CPO的技术优化方向。- Y12T87 Nvidia:降低微环刻蚀工艺误差产生的波长敏感性

前言很长,是Workshop在讨论AI组网下一代,到底用什么封装结构。今天的标题是Arista的观点,延续了他家对于对于LPO的看法,采用传统的热插拔,并且去掉DSP来降低功耗。2026年提出,Y12T86 12.8T的热插拔XPO的封装,是LPO无DSP的12.8T封装。XPO可支持内置的集成商液冷,支持200Gbps PAM4的每通道的高速信号调制,支持64通道的并行工作。也沿用热插拔产业链的成熟性,快速满足市场对于大带宽大容量的需求。而CPO要想实现商用,还需要时间来解决制造工艺以及产业链的困难,之前大家比较纠结的可靠性困境,目前已经基本形成共识是可以解决并得到验证的。Arista虽然更倾向于热插拔的传统结构,但也认为CPO与热插拔并非替代关系,而是可“共存”的关系。下一代AI光学组网,产业链一部分厂家会选择CPO,另一部分厂家会选择XPO的热插拔结构,二者不冲突。4月11日,《人工智能AI大算力驱动的高速光模块/引擎发展趋势》三个小时,可详询18140517646

转载说明:本文系转载内容,版权归原作者及原出处所有。转载目的在于传递更多行业信息,文章观点仅代表原作者本人,与本平台立场无关。若涉及作品版权问题,请原作者或相关权利人及时与本平台联系,我们将在第一时间核实后移除相关内容。

产业数据库

产业链 200+

产业环节 10000+

产业数据 100亿+