3D 芯片时代,等离子刻蚀将走向何方?

专属客服号

微信订阅号

大数据治理

全面提升数据价值

赋能业务提质增效

与光刻图案化、薄膜形成方法等技术一道,等离子体刻蚀不断动态发展,以满足推动现代社会发展的微电子产业呈指数级增长的需求。本文主要介绍 Future of plasma etching for microelectronics: Challenges and opportunities 这篇综述的主要内容,此综述汇集了从学术届到产业界(TEL、Lam 等)的各领域专家对不同主题的见解,这些主题将塑造未来微电子制造中的等离子体刻蚀技术。综述原文可至文末获取。

等离子体辅助刻蚀(Plasma-assisted etching)是过去 50 年来推动微电子行业取得前所未有的进步的关键技术之一,这类进步通常被描述为摩尔定律(Moore's law)的体现。

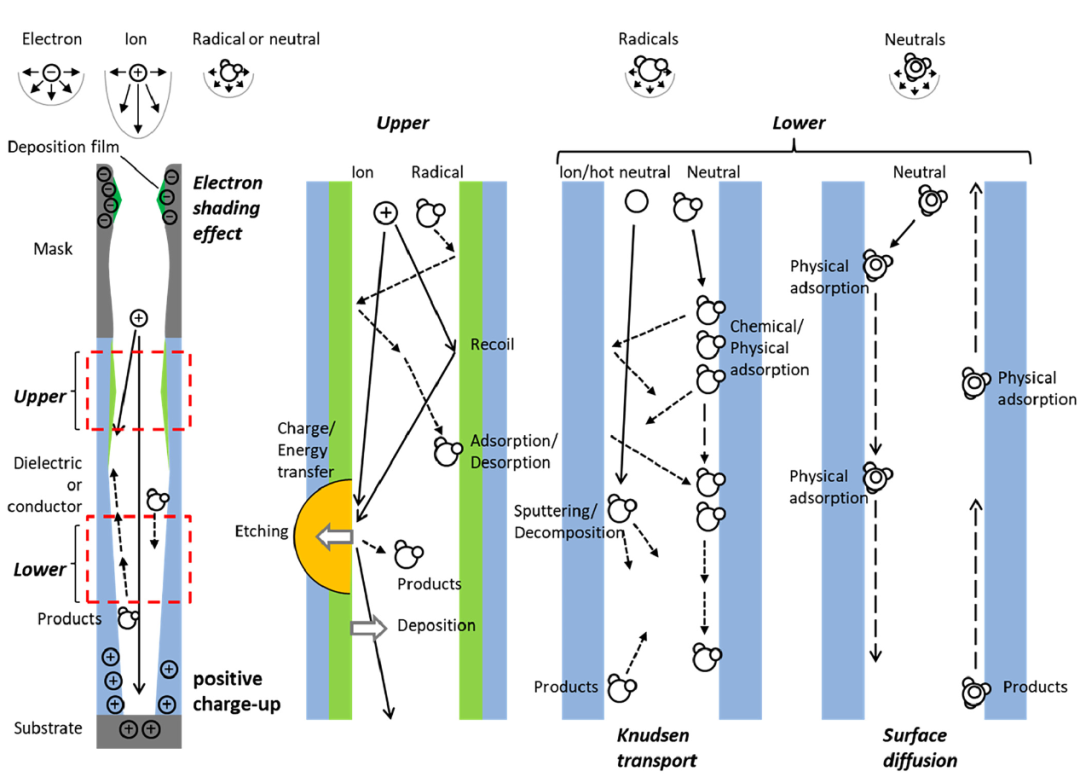

绝缘体和导体中高纵横比孔及结构刻蚀过程的关键反应

正如摩尔(Moore)最初提出的观点,微电子电路性能的指数级提升可通过以下方式实现:几何尺寸上缩小半导体器件及组件、优化器件与电路的缩放比例,以及增大芯片尺寸。这些策略能够在单块硅芯片上集成更多半导体器件,进而实现经济效益。

20 世纪 70 年代,为了制造出各向同性湿法刻蚀技术无法实现的更小尺寸器件,并助力摩尔定律从微米级尺寸最终向纳米级尺寸延伸,等离子体刻蚀(Plasma Etching, PE)技术被引入微电子行业。本质上,等离子体刻蚀是一种在气体等离子体环境中,将光刻定义的光刻胶图案定向且具有材料选择性地转移到构成集成电路的材料中的技术。起初,该技术所涉及的材料主要为硅(Si)、二氧化硅(SiO₂)、氮化硅(Si₃N₄)和铝(Al),但如今已扩展到元素周期表中的多种元素。

等离子体刻蚀技术在微电子领域的未来发展将受到多重因素驱动:随着硅基器件逐渐逼近性能极限,半导体行业的制造需求不断演变;半导体行业面临的人才短缺问题;向更可持续的生产模式转型并满足相关环境法规要求;以及在技术领域具备经济可行性的创新方向。由于技术路径、监管环境和经济因素存在诸多不确定性,目前无法对等离子体刻蚀技术的所有未来发展方面做出明确描述。

本文的目标是明确等离子体刻蚀技术面临的科学挑战,并指出可能在未来微电子制造中发挥关键作用的高效等离子体刻蚀技术方案。这些全新的挑战背后也蕴藏着重大的新机遇 —— 我们将借助过去 50 年等离子体刻蚀技术发展过程中未曾出现过的创新解决方案来应对这些挑战。为深入阐述这些观点,本文汇集了各领域专家的见解,探讨了将塑造未来微电子制造领域等离子体刻蚀技术发展的各类主题。这些专家贡献将简要回顾相关领域的现状,并指出其中的需求与机遇。

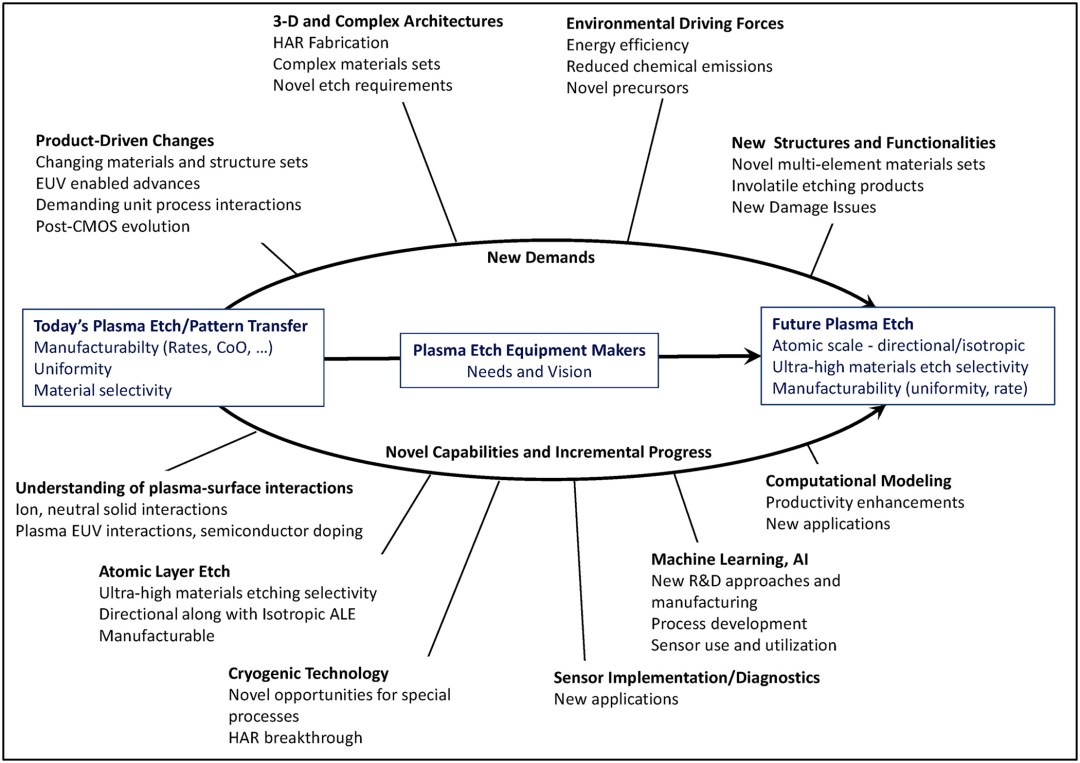

等离子体刻蚀技术的未来发展路径将由颠覆性创新与持续性改进共同塑造,二者并行推进,既要能够制造出未来所需但目前尚未明确形态的半导体产品,又要满足未来社会对可持续性的要求。本文试图阐明这一转型过程中的关键方面,而这一转型需要多个学科与技术方法的深度融合。这种融合关系如下图所示,该图直观呈现了本文各小节所探讨的主题如何共同构成对这一必要转型核心方面的全面综述。

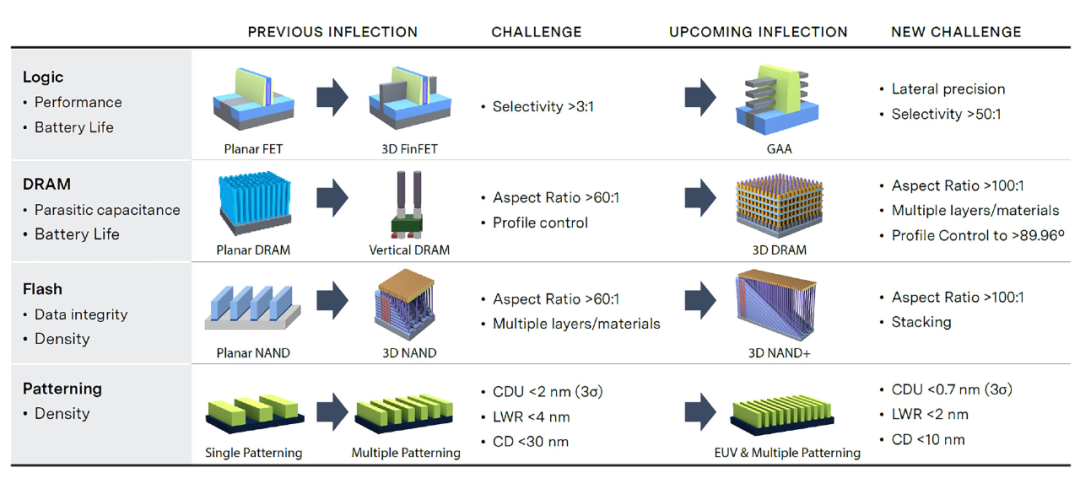

文章首先将从多个行业视角切入,包括基于器件与电路预期发展趋势的等离子体刻蚀技术需求分析。微电子最终产品的生产需经过一系列高度精密的连续工艺,其中包含多个等离子体刻蚀步骤。

影响未来等离子体蚀刻技术的驱动因素与工艺挑战概述。新型能力与渐进式进步将共同应对这些挑战,而等离子体蚀刻设备供应商关于制造需求及潜在解决方案的愿景,进一步补充了这些要求。

接下来,文章综述了近期直接印刷极紫外(EUV)图案转移技术的引入对特定应用场景中等离子体刻蚀工艺产生的影响,并阐述等离子体刻蚀步骤与整体工艺集成流程协同优化所需考虑的典型因素。

随后,本文将探讨与复杂三维结构相关的等离子体刻蚀挑战,包括绝缘体和导体的高纵横比(HAR)加工。紧接着,将围绕绿色化学及环境问题展开讨论,涉及化学前驱体与排放物等影响未来等离子体刻蚀化学体系的关键因素。后 CMOS(互补金属 - 氧化物 - 半导体)技术的演进可能需要新的结构和材料功能,这也将催生更为复杂的材料体系。本文还将介绍针对这类材料(包括刻蚀产物不挥发的材料)进行等离子体刻蚀时需特别考虑的问题。

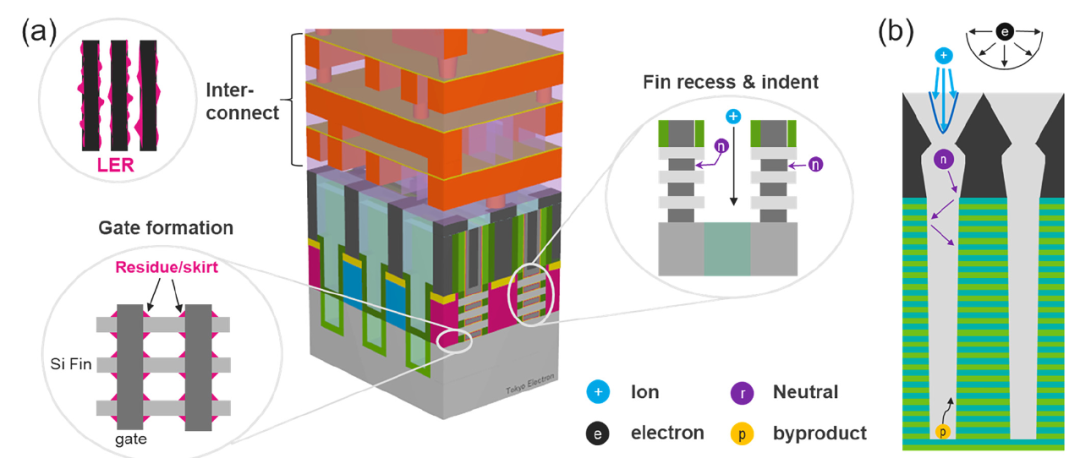

等离子体蚀刻在(a)逻辑栅极全环绕(GAA)晶体管和(b)存储类 3D-NAND 应用中的挑战示例。在 GAA 晶体管制造过程中,蚀刻工艺需制备兼具超高选择性、方向性和轮廓完整性的垂直与水平结构,需将亚 10 纳米尺度结构边角处的残留物及表面粗糙度降至最低。在金属线制备过程中,线边缘粗糙度(LER)的控制至关重要。对于存储类应用,等离子体蚀刻的挑战源于高纵横比(HAR)结构内各类粒子的传输问题,包括离子(+)、中性粒子(n)、蚀刻副产物(p)和电子(e)。

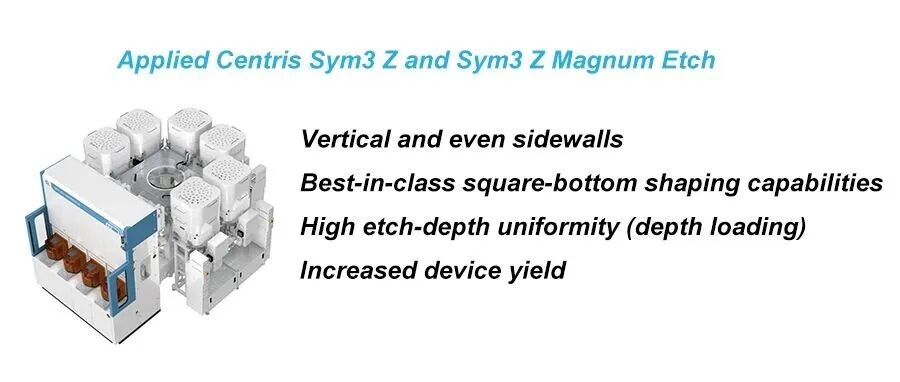

之后,文章呈现三家主要等离子体刻蚀设备供应商的专家观点,阐述他们对微电子领域未来等离子体刻蚀技术需求的看法,以及实现该技术的创新思路。

多项近期创新有望直接推动这些长期存在的等离子体刻蚀挑战的解决,文章重点强调这些机遇。其中包括:对干法刻蚀过程中等离子体 - 表面相互作用的基础理解的深化;等离子体产生的紫外(UV)和真空紫外(VUV)辐射在表面的作用及掺杂效应的研究进展。

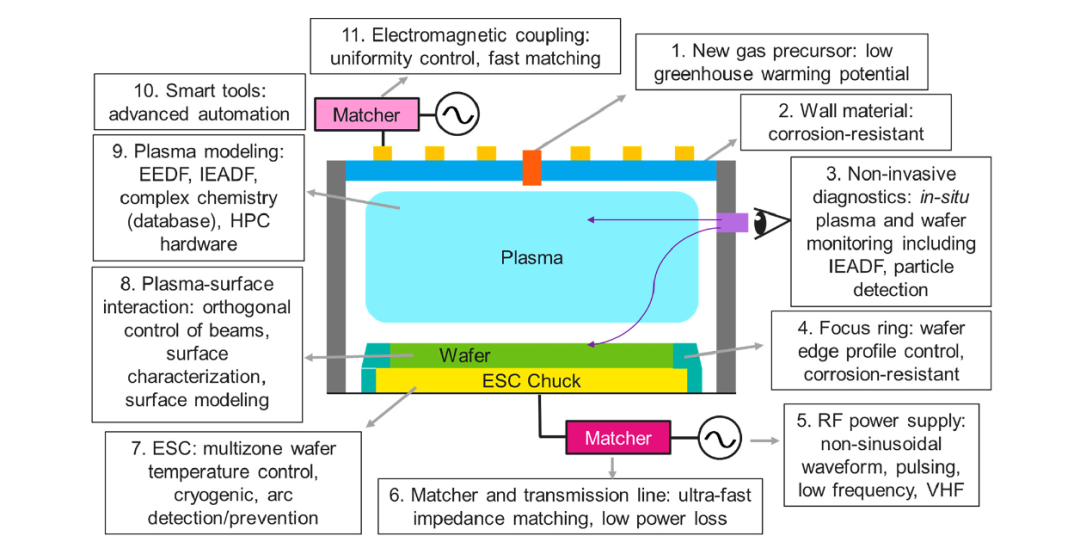

等离子体处理腔室示意图,标注了为应对未来器件缩放及新型架构挑战而需开展技术改进的关键部位。

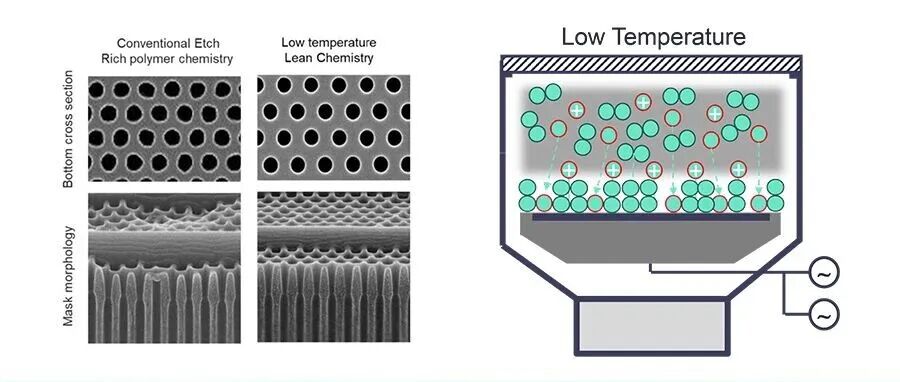

表面工艺的控制可受益于原子层刻蚀(ALE)等技术 —— 该技术能实现超高的材料刻蚀选择性,而等离子体低温刻蚀技术则可优化材料选择性与刻蚀速率控制。通过实时诊断与计量技术,可实现对半导体等离子体刻蚀的精准控制;机器学习则为该领域的研发工作提供了新的思路,同时也能更有效地实现等离子体刻蚀的过程监测。

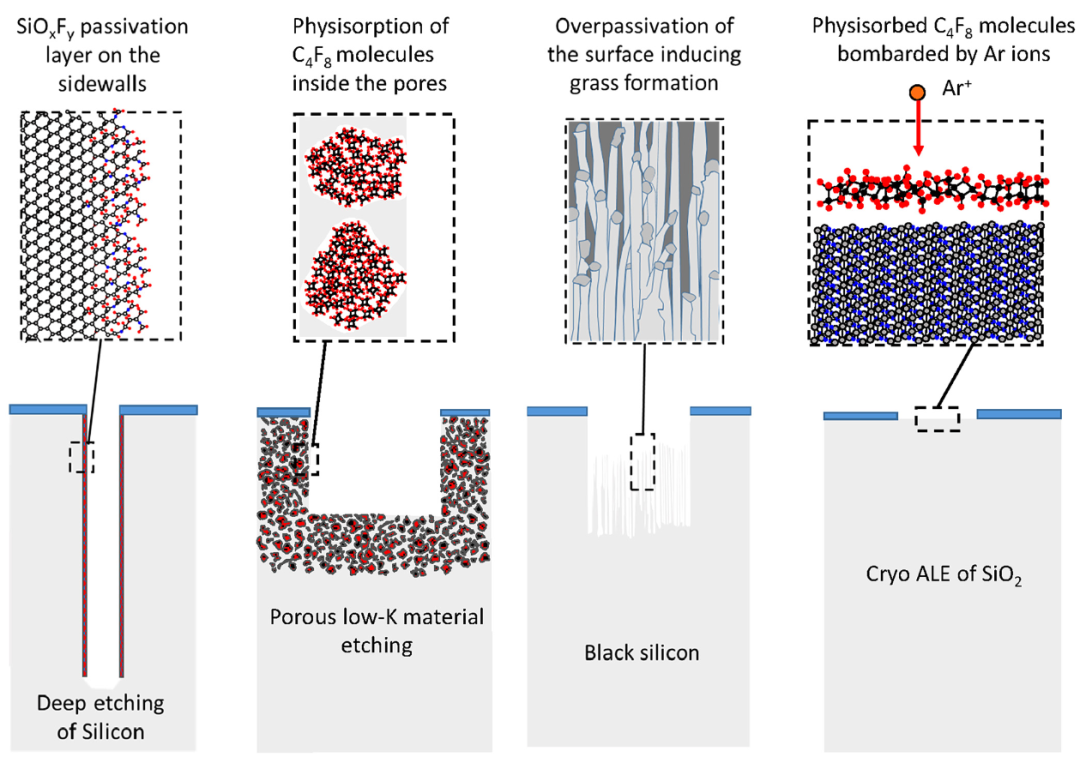

不同用途低温蚀刻工艺所得结构的蚀刻轮廓示意图。(a)硅的深度蚀刻:低温下在侧壁形成氧化氟硅(SiOₓFᵧ)层。(b)多孔低 k 材料的蚀刻:在 - 120℃下通过四氟环丁烷(C₄F₈)气体在孔隙内凝结,降低等离子体诱导损伤(PID)。(c)黑硅制备:在过钝化状态下产生微掩模效应,使硅表面形成 “草状” 结构。(d)二氧化硅(SiO₂)的低温原子层蚀刻(Cryo-ALE):通过分子在表面的物理吸附实现。

最后,先进的反应器与特征尺度计算建模技术如今具备了前所未有的强大能力,能够直接影响实际等离子体反应器的设计、研发以及工艺优化,实现对刻蚀特征的原子级控制。

需要说明的是,本文并未详细探讨等离子体刻蚀领域的所有重要挑战。例如,为了进一步利用建模与计算机仿真助力等离子体刻蚀技术发展,业界迫切需要建立等离子体 / 气体的化学数据库(涵盖电子碰撞过程和重粒子过程),明确表面吸附系数、表面反应速率以及表面建模中的原子间势函数,同时解决多尺度仿真中的误差传递控制问题。这些需求与挑战在本文各小节中仅被简要提及,但即便未展开详细描述,也值得相关研究者重点关注。

获取全文可访问原文链接或私信后台回复关键词:刻蚀。

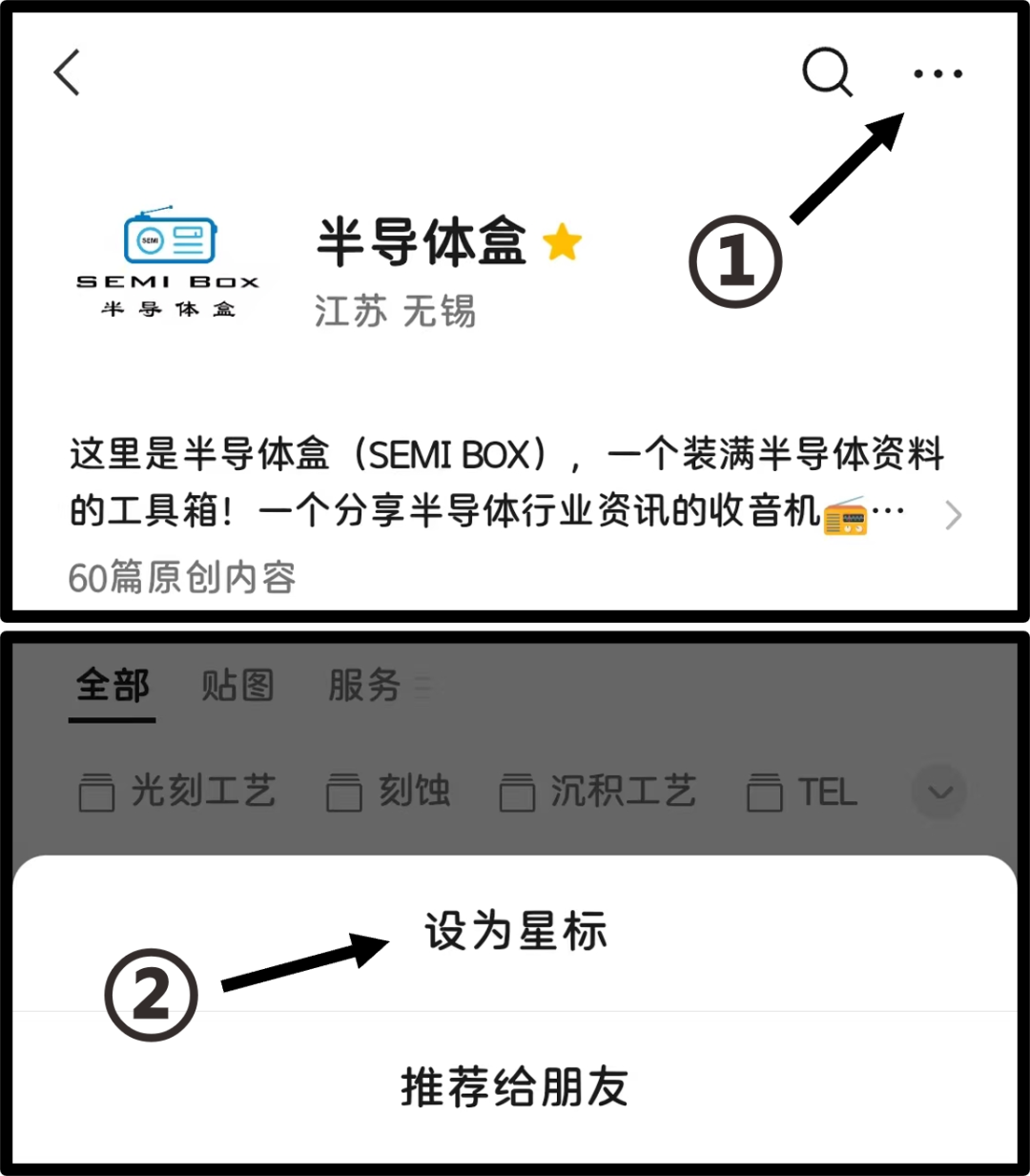

↓设置星标,精彩不错过↓

↓扫一扫,总一款适合你↓

本文仅作行业信息分享、技术交流与岗位对接使用,不涉及任何涉密内容。

欢迎关注本公众号,获取更多半导体设备、工艺、产业动态与优质岗位信息。

如有疏漏、内容建议或岗位咨询,欢迎留言交流。